Pesquisadores da UFRN desenvolvem método para aumentar a eficiência energética de chips de processadores

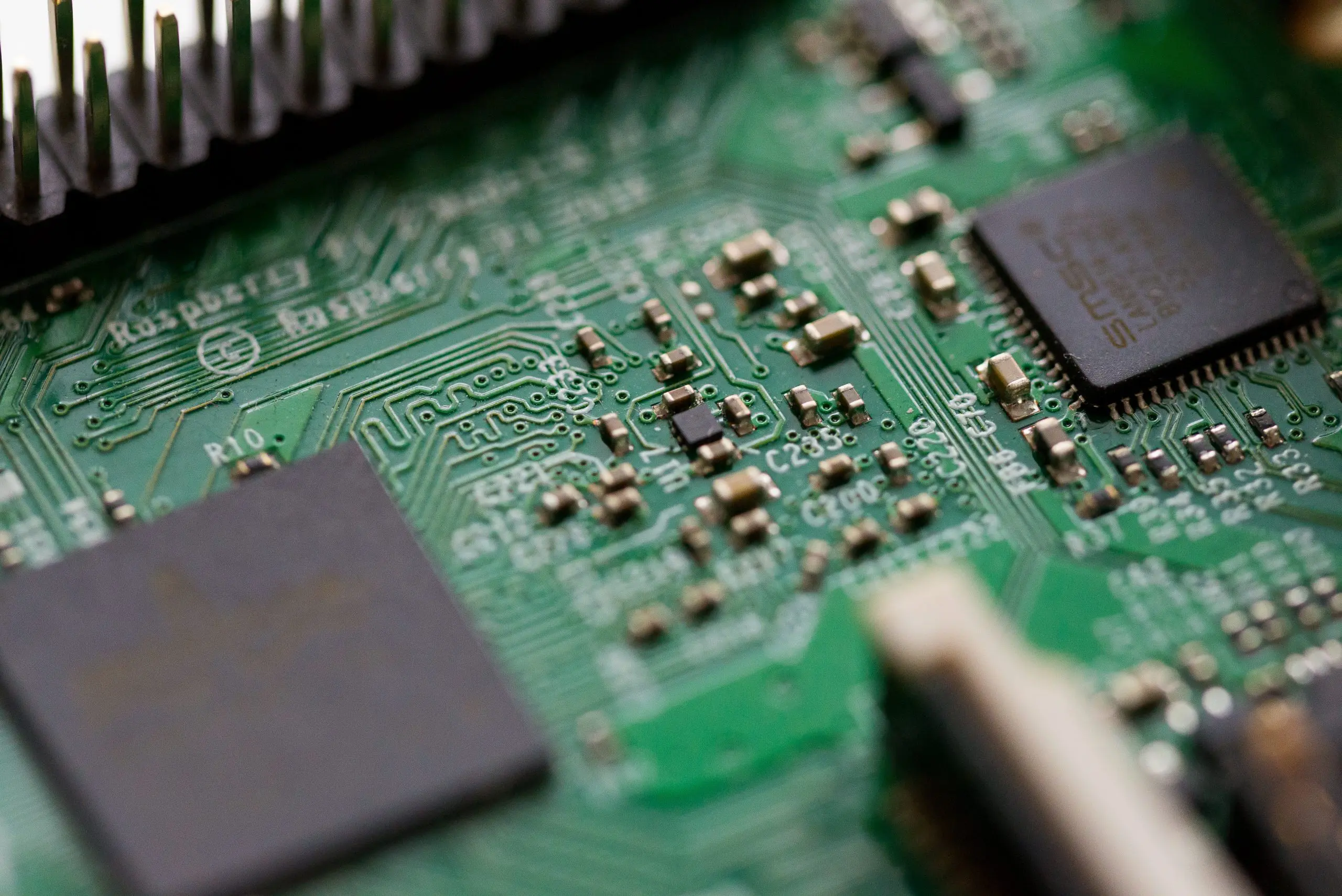

Por Higor Silva em Portal da UFRN | Sistemas embarcados são componentes que processam dados e atuam em conjunto dentro de diversos dispositivos. São encontrados em praticamente todos os âmbitos da tecnologia, como em computadores pessoais (PCs), celulares, TVs, video games, entre outros. Porém, a eficiência energética desses componentes é restrita e, por isso, coisas como o tamanho da bateria e a autonomia da energia costumam sofrer limitações. O professor Samuel Xavier de Souza, do Departamento de Engenharia da computação e Automação (DCA/UFRN) e coordenador do Núcleo de Processamento de Alto Desempenho (NPAD/UFRN), é um dos responsáveis por uma pesquisa que visa encontrar soluções para esse problema.

Desenvolvido no Laboratório de Arquiteturas Paralelas para Processamento de Sinais (LAPPS/UFRN), filiado ao Instituto Metrópole Digital (IMD/UFRN), o estudo faz parte da pesquisa de doutorado de Diego Cirilo do Nascimento, no Programa de Pós-Graduação em Engenharia Elétrica e de Computação (PPgEEC / UFRN). A ideia da pesquisa nasceu durante visita de Diego à Universidade de Bristol, na Inglaterra, onde foi possível firmar uma colaboração com a professora Kerstin Eder e o pesquisador de pós-doutorado Kyriakos Georgious, que é supervisionado por ela.

Um dos fatores principais dessa limitação dos sistemas embarcados são as margens de segurança, usadas pelo DVFS (Dynamic Voltage and Frequency Scaling) para definir e controlar as tensões e frequências dos processadores. Essa limitação existe para que não haja erros computacionais. A questão é que algumas diferenças são encontradas após a montagem de cada processador, assim, os circuitos em cada chip são distintos uns dos outros, mas esses limites de segurança são os mesmos. Desse modo, os dispositivos são ajustados para a pior hipótese, levando em consideração todos os processadores, e, quanto maior a margem, mais energia se gasta, gerando muito consumo desnecessário.

A pesquisa comprova a existência de um valor exagerado na margem de segurança em chips de sistemas embarcados, que já são seguros e energeticamente eficientes. Com essa confirmação, existe agora um motivo para utilizar técnicas energeticamente mais eficientes, como a de detecção e correção de erros, muito utilizadas em chips de satélites espaciais, que podem sofrer eventuais erros causados pela radiação. “Ou seja, diminuiremos as margens até o limite do acontecimento de erros e, caso aconteçam, corrigimos esses erros, tentando sempre evitá-los mantendo as margens no limite, mas sem ultrapassá-lo”, explica o professor Samuel Xavier.

Ao investigar as margens dos chips, a equipe detectou o ponto onde esses dispositivos poderiam falhar, delimitando a fronteira em que há e não há erros. Assim, observaram o tamanho da margem real necessária para aquele componente em relação à tensão e frequência em diferentes configurações. Foi observado que, em determinadas configurações, é possível se elevar a frequência até 2,5 vezes o normal sem o registro de erros.

Economia de energia e aumento de desempenho, isso define o potencial dos resultados dessa pesquisa. Com um futuro cada vez mais conectado e tecnológico, o impacto de um estudo que busca sustentabilidade e eficiência é essencial. “Com a estimativa de as tecnologias da informação e comunicação alcançarem o consumo de um quinto da energia produzida no planeta até 2030, esse ganho pode ser muito significativo, qualquer que ele seja, por causa da massa de dispositivos que pode alcançar”, completa o professor Samuel Xavier.

Este texto foi originalmente publicado pelo Portal da UFRN de acordo com a licença Creative Commons CC-BY-NC-ND. Leia o original. Este artigo não necessariamente representa a opinião do Portal eCycle.